- #SYNPLICITY SYNPLIFY PRO DOWNLOAD SOFTWARE INSTALL#

- #SYNPLICITY SYNPLIFY PRO DOWNLOAD SOFTWARE SOFTWARE#

- #SYNPLICITY SYNPLIFY PRO DOWNLOAD SOFTWARE LICENSE#

#SYNPLICITY SYNPLIFY PRO DOWNLOAD SOFTWARE INSTALL#

STEP 2 - Install each ispLEVER Classic Module Note that the Base Module must be installed prior to the FPGA Module. This optional module adds support for ORCA FPGA and FPSC devices.

It also includes the Lattice version of the Synplify™ Pro synthesis tool (I-2014.03LC) from Synopsys® for HDL synthesis as well as the Mentor ModelSim Lattice Edition. This includes the ispLEVER Project Navigator, and all the tools and device libraries you need to implement a design for any of the programmable families listed at the right.

#SYNPLICITY SYNPLIFY PRO DOWNLOAD SOFTWARE SOFTWARE#

Use the Downloads tab on this page to download the software installers.

IspLEVER Classic consists of the modules as listed below The ispLEVER Classic Base Module installation (which includes Synplify Synthesis module and Mentor ModelSim Lattice Edition for simulation) and the ispLEVER Classic FPGA Module installation.

#SYNPLICITY SYNPLIFY PRO DOWNLOAD SOFTWARE LICENSE#

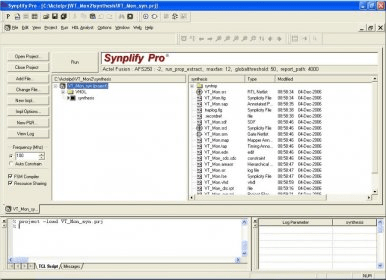

To continue with the Synplify design flow, assign design constraints with the Synplify software.Follow the three steps below to Download, Install, and License ispLEVER Classic. This option decreases area but might also decrease performance. Turn on Resource Sharing in the Synplify window. Turning on this option may reduce unnecessary states and transitional logic. To direct the Synplify software to automatically find and re-encode state machines in your design, turn on Symbolic FSM Compiler in the Synplify window. Type the frequency value for the project in the Frequency (MHz) box in the Synplify window. To change the results directory, type the name of the new directory in the Results Directory box. For Synplify version 6.0 and later, the output files are generated by default into the rev_1 directory. To specify the format for Synplify-generated output files, select vqm in the Result Format box. Under Device Mapping Options, turn on Map logic cells to ATOMS. In the Package list, select the device package. In the Speed list, select an appropriate speed grade. In the Technology list, select the device family. The Options for implementation dialog box appears. If the design uses functions from the altera.v library, add the library file name to the top of the Source Files list in the Synplify window. vhd) generated by the MegaWizard Plug-In Manager in your project. If you created and instantiated an LPM function in your design, you must also include the Verilog Design File (. To create a hierarchical project, select the top-level design file in the Files to Add to Project list and drag it to the bottom of the list. To add the files in the Files To Add To Project list in the Synplify window, click Add.

Select one or more design files to add to the project in the Select Files to Add to Project dialog box. In the File Type list, select Project File (Project). To create and add files to a new project: To start the Synplify software on a Windows system, type synplify at a command prompt, or double-click the synplify.exe icon. To start the Synplify software on a Linux workstation, type synplify at a command prompt from your working directory. If you have not already done so, create a design for use with the Synplify software. To setup a project in the Synplify software: Setting up a project in the Synopsys Synplify software includes starting the Synplify software, creating the project and adding files, and selecting a target device and output settings. Setting Up a Project with the Synplify Software

0 kommentar(er)

0 kommentar(er)